1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

|

void dump_scb()

{

uint32_t icsr = SCB->ICSR;

uint32_t shcsr = SCB->SHCSR;

printf("ICSR:\r\n");

printf("\t there %s interrupt pending\r\n",

(icsr & SCB_ICSR_ISRPENDING_Msk) ? "is" : "isn't");

printf("\t pending exception number:%u\r\n",

(icsr & SCB_ICSR_VECTPENDING_Msk) >> SCB_ICSR_VECTPENDING_Pos);

printf("\t active exception number:%u\r\n",

(icsr & SCB_ICSR_VECTACTIVE_Msk) >> SCB_ICSR_VECTACTIVE_Pos);

printf("SHPRx:\r\n");

printf("\t Mem Manage:%hhd\r\n", (SCB->SHP[0] & PRIORITY_Msk) >> PRIORITY_Pos);

printf("\t Bus Fault:%hhd\r\n", (SCB->SHP[1] & PRIORITY_Msk) >> PRIORITY_Pos);

printf("\t Usage Fault:%hhd\r\n", (SCB->SHP[2] & PRIORITY_Msk) >> PRIORITY_Pos);

printf("\t SVC:%hhd\r\n", (SCB->SHP[7] & PRIORITY_Msk) >> PRIORITY_Pos);

printf("\t Debug Monitor:%hhd\r\n", (SCB->SHP[8] & PRIORITY_Msk) >> PRIORITY_Pos);

printf("\t PendSV:%hhd\r\n", (SCB->SHP[10] & PRIORITY_Msk) >> PRIORITY_Pos);

printf("\t SysTick:%hhd\r\n", (SCB->SHP[11] & PRIORITY_Msk) >> PRIORITY_Pos);

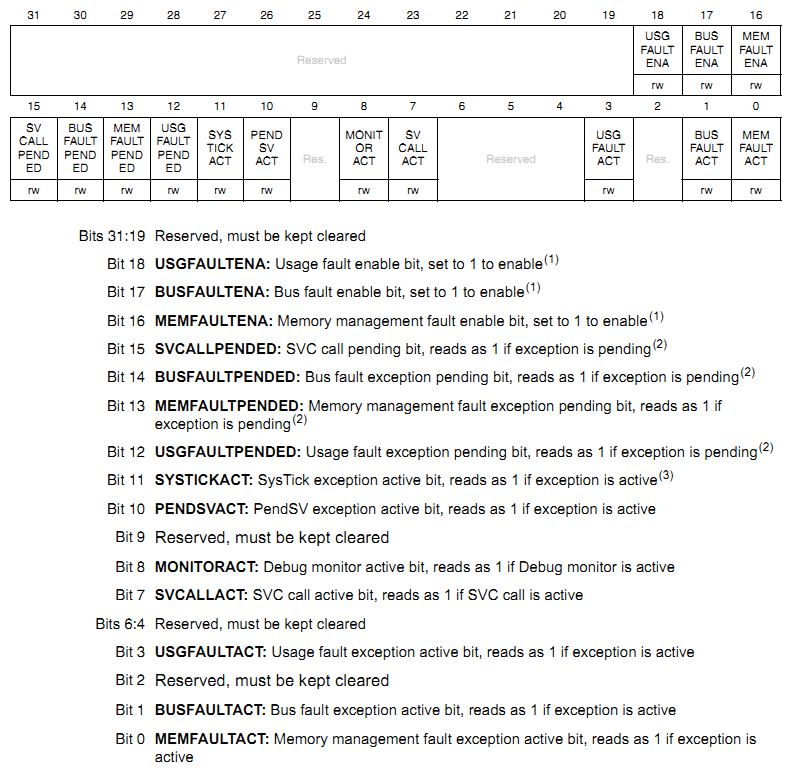

printf("SHCSR:\r\n");

printf("\t Usage Fault enable:%u\r\n",

(shcsr & SCB_SHCSR_USGFAULTENA_Msk) >> SCB_SHCSR_USGFAULTENA_Pos);

printf("\t Bus Fault enable:%u\r\n",

(shcsr & SCB_SHCSR_BUSFAULTENA_Msk) >> SCB_SHCSR_BUSFAULTENA_Pos);

printf("\t Mem Fault enable:%u\r\n",

(shcsr & SCB_SHCSR_MEMFAULTENA_Msk) >> SCB_SHCSR_MEMFAULTENA_Pos);

printf("\r\n");

printf("\t SVCall pended:%u\r\n",

(shcsr & SCB_SHCSR_SVCALLPENDED_Msk) >> SCB_SHCSR_SVCALLPENDED_Pos);

printf("\t Bus Fault pended:%u\r\n",

(shcsr & SCB_SHCSR_BUSFAULTPENDED_Msk) >> SCB_SHCSR_BUSFAULTPENDED_Pos);

printf("\t Mem Fault pended:%u\r\n",

(shcsr & SCB_SHCSR_MEMFAULTPENDED_Msk) >> SCB_SHCSR_MEMFAULTPENDED_Pos);

printf("\t Usage Fault pended:%u\r\n",

(shcsr & SCB_SHCSR_USGFAULTPENDED_Msk) >> SCB_SHCSR_USGFAULTPENDED_Pos);

printf("\r\n");

printf("\t SysTick active:%u\r\n",

(shcsr & SCB_SHCSR_SYSTICKACT_Msk) >> SCB_SHCSR_SYSTICKACT_Pos);

printf("\t PendSV active:%u\r\n",

(shcsr & SCB_SHCSR_PENDSVACT_Msk) >> SCB_SHCSR_PENDSVACT_Pos);

printf("\t Monitor active:%u\r\n",

(shcsr & SCB_SHCSR_MONITORACT_Msk) >> SCB_SHCSR_MONITORACT_Pos);

printf("\t SVCall active:%u\r\n",

(shcsr & SCB_SHCSR_SVCALLACT_Msk) >> SCB_SHCSR_SVCALLACT_Pos);

printf("\t Usage Fault active:%u\r\n",

(shcsr & SCB_SHCSR_USGFAULTACT_Msk) >> SCB_SHCSR_USGFAULTACT_Pos);

printf("\t Bus Fault active:%u\r\n",

(shcsr & SCB_SHCSR_BUSFAULTACT_Msk) >> SCB_SHCSR_BUSFAULTACT_Pos);

printf("\t Mem Fault active:%u\r\n",

(shcsr & SCB_SHCSR_MEMFAULTACT_Msk) >> SCB_SHCSR_MEMFAULTACT_Pos);

}

void dump_ufsr()

{

uint16_t ufsr = (SCB->CFSR & SCB_CFSR_USGFAULTSR_Msk) >> SCB_CFSR_USGFAULTSR_Pos;

printf("UFSR:\r\n");

printf("\t Divide by zero: %d\r\n",

(ufsr & DIVBYZERO_Msk) >> DIVBYZERO_Pos);

printf("\t Unaligned access: %d\r\n",

(ufsr & UNALIGNED_Msk) >> UNALIGNED_Pos);

printf("\t No coprocessor: %d\r\n",

(ufsr & NOCP_Msk) >> NOCP_Pos);

printf("\t Invaild PC load: %d\r\n",

(ufsr & INVPC_Msk) >> INVPC_Pos);

printf("\t Invaild state(attempt to entry ARM state): %d\r\n",

(ufsr & INVSTATE_Msk) >> INVSTATE_Pos);

printf("\t Undefined instruction: %d\r\n",

(ufsr & UNDEFINSTR_Msk) >> UNDEFINSTR_Pos);

}

|